Hello, I’m using TLE9201SG to drive a window motor with TMS320. When I transferred a diagnostic read signal (0x00), it returned me the default diagnostic signal (0xDF), but after that thing got messy and I only started getting repeated messages, for ...Read more

Hello,

I’m using TLE9201SG to drive a window motor with TMS320. When I transferred a diagnostic read signal (0x00), it returned me the default diagnostic signal (0xDF), but after that thing got messy and I only started getting repeated messages, for example when I transferred 0xC0 it transferred back 0xC0 when I transferred 0xA0 it returned 0xA0. Things start to go easily if I just use the WR_CTRL_RD_DIA command, but when I send an RD_DIA command or a wrong command, it gets stuck in this repeated message hell.

How can I solve this?

Thank You

Read less

Hello, It sounds like you may be experiencing some communication errors with your TLE9201SG. When you are receiving repeated messages, it could be due to noise on the communication line or incorrect timing of the signals. Here are some steps you can take to troubleshoot the issue: Check your timing:Read more

Hello,

It sounds like you may be experiencing some communication errors with your TLE9201SG. When you are receiving repeated messages, it could be due to noise on the communication line or incorrect timing of the signals.

Here are some steps you can take to troubleshoot the issue:

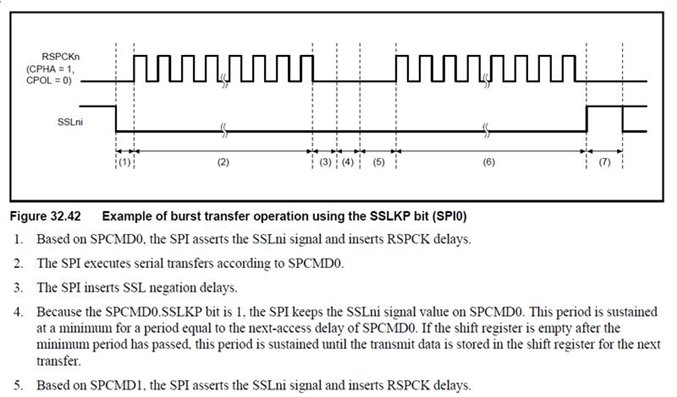

Check your timing: Verify that you are sending the commands at the correct time. The TLE9201SG uses SPI communication, and the timing requirements are critical. Make sure that you are following the timing requirements specified in the datasheet, and that the clock signal is stable and accurate.

Check for noise: Noise on the communication line can cause errors in data transmission. Use an oscilloscope or logic analyzer to check for noise on the communication lines. If you see noise, try adding decoupling capacitors to the power and ground lines, or consider adding a filter to the communication lines.

Check your commands: Double-check that you are sending the correct commands to the TLE9201SG. Sending incorrect commands can cause the device to get stuck in a loop or return unexpected data. Refer to the datasheet for the correct command codes and data formats.

If none of these steps resolve the issue, you may want to consider contacting the manufacturer for further assistance or replacing the TLE9201SG.

Thank You

See less