Hello, I have an R7FA2E1A93CFM microcontroller set as a slave. I use SCI SPI. The miso side of the communication line creates a pointless pulse. Functions that shouldn’t work are triggered because of this signal. You can see it in the ...Read more

Hello,

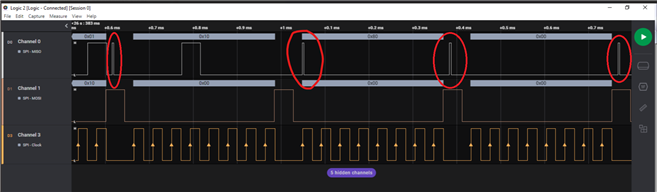

I have an R7FA2E1A93CFM microcontroller set as a slave. I use SCI SPI. The miso side of the communication line creates a pointless pulse. Functions that shouldn’t work are triggered because of this signal. You can see it in the circle in the picture below. I need your help.

Thank You in Advance…

Read less

Hi, The MISO pulses manifest at some stage in SPI idle state (while the clock is idle among the transfers). In master mode (in SPI, now no longer SCI_SPI) there's the choice to pick out MOSI idle level at low or high based on the MOIFE and MOIFV bit settings in SPPCR. However, there's no such choiceRead more

Hi,

The MISO pulses manifest at some stage in SPI idle state (while the clock is idle among the transfers).

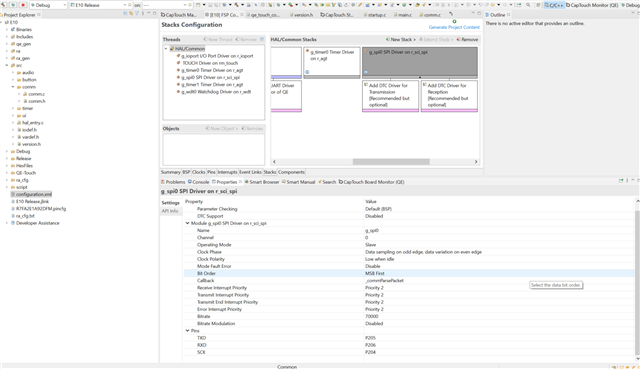

In master mode (in SPI, now no longer SCI_SPI) there’s the choice to pick out MOSI idle level at low or high based on the MOIFE and MOIFV bit settings in SPPCR.

However, there’s no such choice in slave mode to choose the idle level of MISO.

We could help greater in case you share more information about why those pulses are trouble to your application.

Regards,

Nidhi

See less