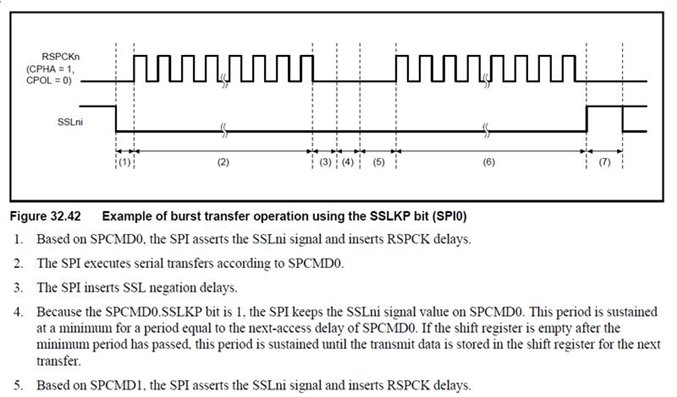

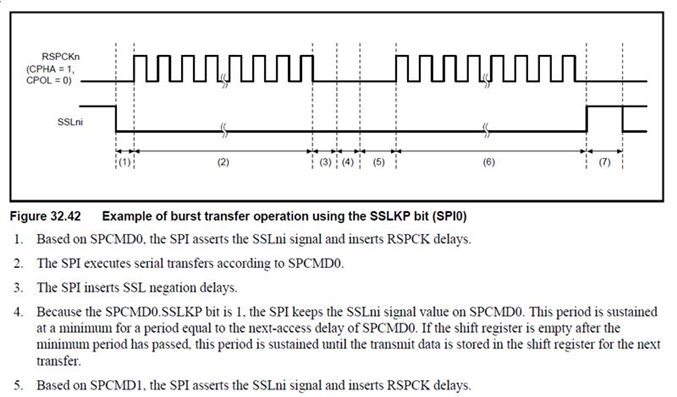

I’m using Renesas FSP to set up the SPI module of an RA4W1 EVK as Master. I’m using burst mode( no negation of the SS between bytes) and there’s an”inter-byte” delay, as shown in figure below( taken from the MCU datasheet). Is there anyway to get relieve of this delay? I know FSP allows setting the values for timepiece delay, SS negation delay, and coming access delay, but their minimal value is SPI_DELAY_COUNT_1, which results in a delay of 3 CLK cycles between bytes. Some SPI Slaves allow nonstop timepiece with no delay between bytes, which results in advanced outturn.

Thanks for any help you can give!